Руководство к практическим занятиям по автоматизированному проектированию аналого-цифровых схем

2.3.

Проектирование

Вспомогательных

элементов

цифровых

узлов

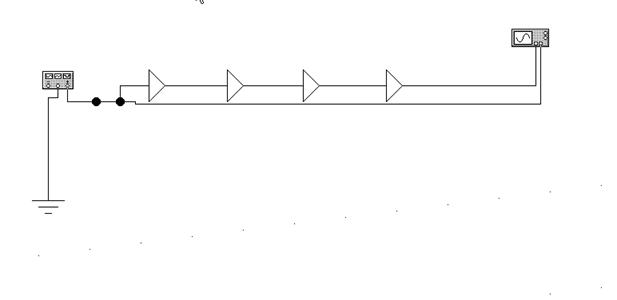

I.

Используя

математический

пакет Electronics Workbench

собрать

схему на N

буферных

элементах

для задержки

сигнала вида:

где

N- номер по

списку.

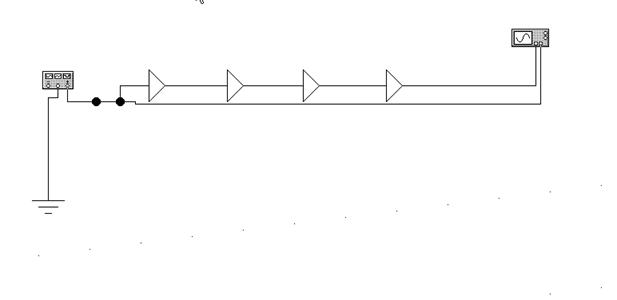

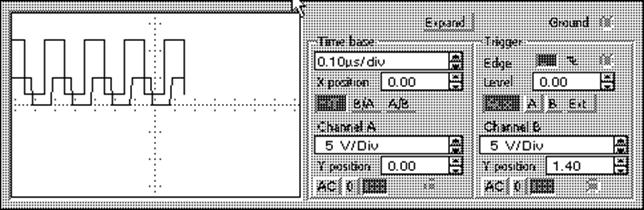

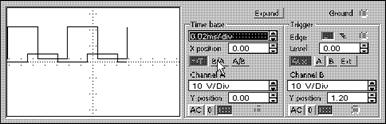

На

осциллографе

получить

сигнал вида

Определить

время

задержки

сигнала

одного

буферного

элемента.

II.

III.

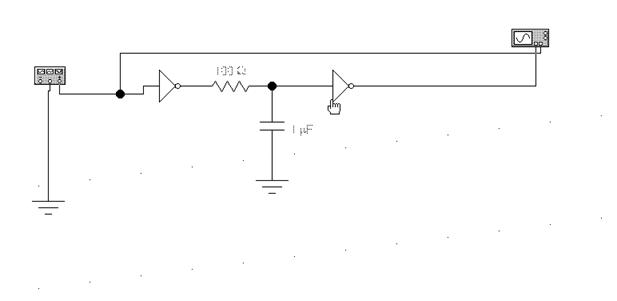

Для задержки

сигнала

собрать

схему на

инверторах с

RC цепочкой

вида:

Номинал

сопротивления

равен N кОм,

где N- номер по

списку.

На

осциллографе

получить

сигнал вида

Определить

время

задержки

сигнала.

Примечание:

Частота

генератора

задается с

учетом

оценочного

времени

задержки RC

цепочки

равного 0.7 RC.

IV.

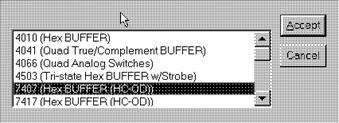

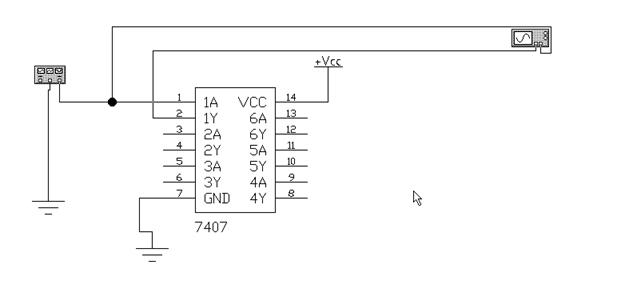

Для задержки

сигнала

собрать

схему на N

буферных

элементах 7407 (Hex BUFFER

(HC-OD))

вида:

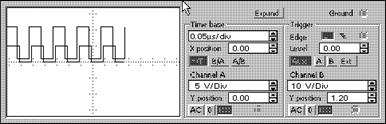

На

осциллографе

получить

сигнал вида

Определить

суммарное

время

задержки

сигнала.